- 半導体業界トレンド情報#52

先進パッケージング技術の進化

1.先進パッケージングが牽引する「ポスト微細化」時代

半導体の微細化がかつてのようなペースでは進まなくなってきている一方で、AIサーバーや自動運転、5G基地局などの分野では、計算性能と省電力性の両立がこれまで以上に求められる状況となっている。

従来は単一の大きなチップを微細化して性能向上を図るアプローチが主流だったが、現在はリーク電流や製造コスト、歩留まりの悪化が課題として顕在化している。このため、複数のチップを空間的に組み合わせ、システム全体で性能と消費電力のバランスを最適化する「先進パッケージング技術」が重要な役割を担うようになってきている。

先進パッケージングには、2.5Dパッケージング、3D積層、チップレット技術など複数のアプローチが含まれる。いずれも、ロジックとメモリ、あるいは異なるプロセスノードのチップを高密度に接続し、システムレベルで性能を高めることを狙った技術群となっている。

2.2.5D・3D積層とHBMによるメモリ帯域の拡大

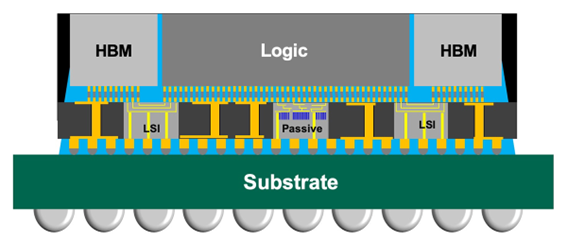

2.5Dパッケージングは、複数の半導体チップ(ダイ)をシリコン製または有機基板製のインターポーザ上に横並びで実装し、チップ間を微細配線で高密度・高速に接続するパッケージ技術を指す。ロジックとメモリを近接配置できることから、特にメモリ帯域がボトルネックとなりやすいAIアクセラレータやHPC向けGPUで重視されている。

TSMCの「CoWoS(Chip on Wafer on Substrate)」は、この2.5Dパッケージングを代表する技術の一つだ。GPUダイとHBMスタックをインターポーザ上に配置し、広幅のインターフェースで接続することで、高帯域かつ低消費電力なメモリアクセスを可能としている。NVIDIAをはじめとするAIアクセラレータの中核パッケージ技術となっており、需要が集中することで供給不足が深刻化している。これを受けて、TSMCは外部OSAT(半導体後工程受託企業)の活用を含めた生産体制の強化を図っている。

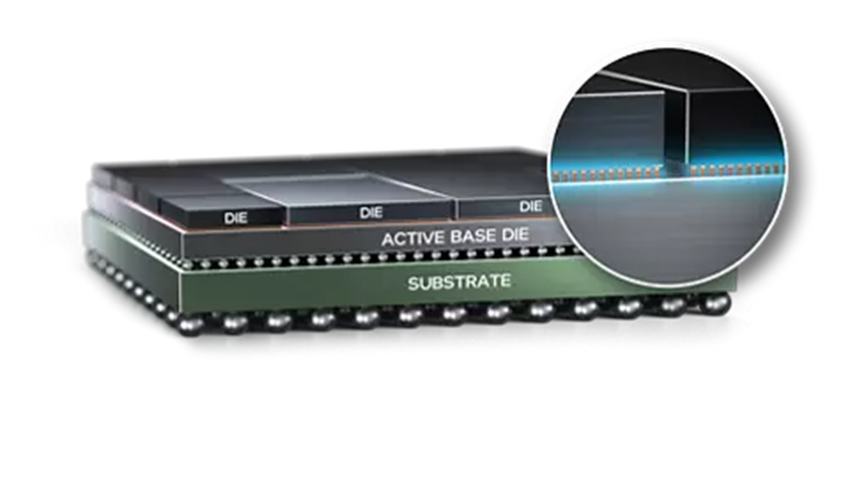

また、3D積層は、複数の半導体チップを上下方向に積み重ね、シリコン貫通電極(TSV)やマイクロバンプなどで接続する技術として発展してきた。近年では、マイクロバンプをさらに小型化したハイブリッドボンディングなども登場し、チップ間配線の長さを大幅に短縮することで、高速かつ低消費電力な信号伝送が可能となっている。

代表的な応用例として、DRAMダイを縦方向に積層したHBM(High Bandwidth Memory)が挙げられる。HBMはロジックチップのすぐ近くに高帯域メモリを配置する構成となっており、AI向けアクセラレータやHPC向けGPUにおいて、メモリ帯域のボトルネックを緩和する手段として広く採用されている。

HBMメーカーの代表企業としては、SK Hynixが挙げられる。同社は2024年に36GBの12段積層HBM3Eを量産開始しており、1.18TB/s級のデータ処理を可能とする高帯域メモリとしてNVIDIA向けに供給している。さらに2025年9月には、世界で初めてHBM4の量産体制を構築したと発表しており、AIサーバー向けメモリのリーダー企業としてのポジションを強めている。

ロジック同士の3D積層技術としては、Intelの「Foveros」が代表的な例の一つに挙げられる。同社はクライアントCPU「Meteor Lake」などで、ベースタイル上にCPUコアタイルやGPUタイルなどを積層し、TSVと微細ピッチ接続(マイクロバンプ等)によって高帯域に接続する構成を採用している。これにより、機能ごとに最適なプロセスノードを使い分けつつ、1パッケージとしての性能・消費電力バランスを高めるアプローチが可能となっている。

3.チップレット技術と異種集積

チップレット技術は、本来一つの大きなSoCとして設計されていた機能ブロックを、複数の小さなチップ(チップレット)に分割し、パッケージ内で高速インターフェースを用いて接続するアプローチだ。

この手法を用いることで、アナログ回路やI/O部などは成熟ノードで製造し、高性能ロジック部は先端ノードで製造するといった「異種プロセスノードの組み合わせ」が可能となる。結果として、開発コストやマスク枚数の削減、歩留まりの向上、設計再利用性の向上が見込まれる。

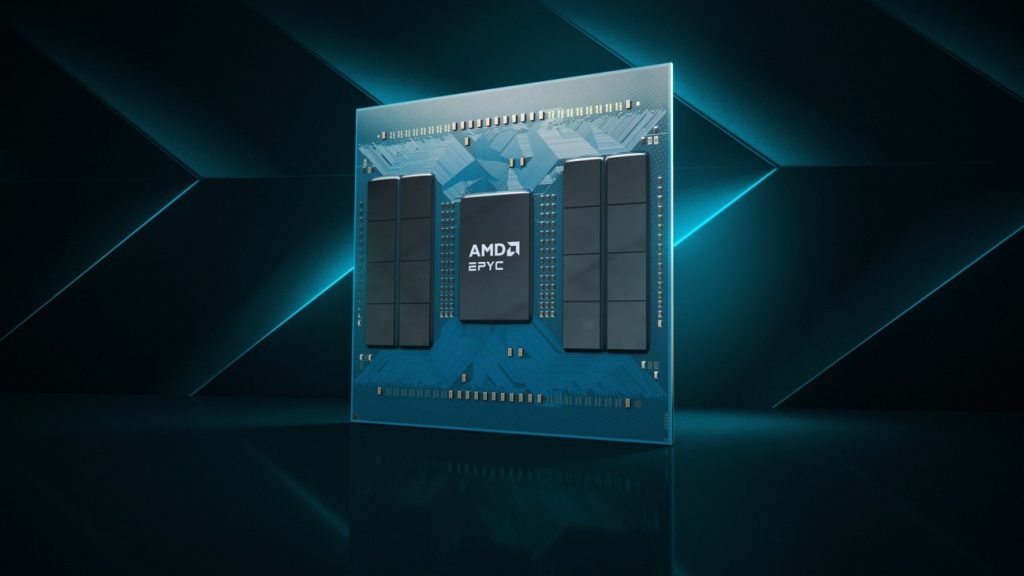

チップレット技術では、AMDが先行している企業の一つに挙げられる。同社のサーバー向けCPU「EPYC」シリーズでは、CPUコア部を複数のCCD(Compute Chiplet Die)として分割し、I/O機能を別ダイに分離したマルチチップ構成を採用。この構造により、先端ノードを用いるコア部と、より成熟ノードで製造するI/O部を組み合わせることでコストと歩留まりの最適化を図っている。

さらに、データセンター向けGPU「Instinct」シリーズでは、先述の2.5Dパッケージング技術を活用しつつ、GPUチップレットとHBMスタックを組み合わせたアーキテクチャを展開している。今後は、ノード内のGPU接続だけでなく、複数ノードをまとめたラック全体までを統一的に接続・制御できる仕組みを立ち上げることで、大規模AI処理に適したプラットフォームの構築を目指す。

なお、AMD自身は設計と製品アーキテクチャに特化したファブレス企業であり、上記のような先端製品はTSMCや各種OSATなどに製造を委託している。

4.先進パッケージングがもたらす産業構造の変化

先進パッケージング技術が普及すると、価値の源泉が「単一ダイの微細化」から「システム全体のアーキテクチャ設計と統合技術」へとシフトしていくものと予測される。

設計面では、パッケージとチップを統合的に最適化する「システムレベルEDA」が重要度を増しており、配線遅延や電源・熱設計を含めた同時最適化が求められるようになっている。製造面では、WLP(ウエハーレベルパッケージング)やファンアウト型パッケージなどを含め、前工程と後工程の境界が曖昧になりつつあり、ファンドリとOSATの役割分担も再定義されつつある。

一方で、先進パッケージングは設備投資額やプロセスの複雑さが増すため、材料や装置、検査技術を含めたサプライチェーン全体での対応が不可欠となっている。特に、熱・機械・電気信頼性を確保しながら歩留まりを安定させることは容易ではなく、各国政府による支援や、産官学連携による研究開発が今後も続くとみられる。

先進パッケージング技術は、単なるパッケージの高機能化にとどまらず、システム設計の自由度を高め、AIやHPC(高性能コンピューティング)、車載向けといった成長市場での競争力を左右する重要な基盤技術となっている。同技術の進化は、今後の半導体産業の勢力図を大きく変えていく可能性があると考えられる。

安部’s EYE

今回のトレンド情報は、「先進パッケージング技術の進化」についてアップさせて頂く。

半導体はチップの微細化と共に進化を続けてきた訳だが、流石に物理的限界が近づく中で微細化のペースもかつてのようには進まなくなっている。しかし性能面では益々要求が高くなっており、従来の“前工程”・“後工程”と言われた産業構造自体に変化が見られるようになってきている。

2024年8月5日にリリースした半導体業界トレンド情報#38でも「パッケージングの最新技術」についてアップしたが、後工程においても前工程のウエハープロセスが用いられる様になって来ており、次第に従来の前工程と後工程の境界が無くなってきており、ファンドリとOSATの役割分担も再定義されつつある。

記事にある先進パッケージング技術は、既に従来の“後工程”の範囲を超越しており、設備投資額やプロセスの複雑さが増すため、材料や装置、検査技術を含めたサプライチェーン全体での対応が不可欠となっている。その中で歩留まりを安定させることは容易ではなく、単なるパッケージの高機能化にとどまらず「システム全体のアーキテクチャ設計と統合技術」が重要となって来る。

“最先端分野”に対する各国政府による支援や、産官学及び企業間連携による研究開発競争の激化は凄まじいスピードで進むことが想定され、今後の半導体産業の勢力図そのものが大きく変わって来るものと思われる。