- 半導体業界トレンド情報#45

半導体の低消費電力化技術

1.半導体の消費電力削減を求められる背景

半導体は、スマートフォンやPC、データセンター、自動車、産業用ロボット、IoTデバイスなど、あらゆる分野で不可欠な存在となっている。これらの機器が高性能化し、膨大なデータを処理するようになるにつれて、消費電力の増加が課題となってきた。

環境意識の高まりやエネルギーコストの上昇、バッテリー駆動時間の延長への要求などを背景に、機器の稼働効率や省エネが重視されるようになった。

これに伴い、半導体の消費電力をいかに低減しながらも高い演算性能を維持するかが、重要な競争力の源泉となっている。

2.低消費電力化に向けた最新技術

半導体の省エネ化を実現するためには、トランジスタ構造や材料、回路設計、パッケージング技術など、多方面での取り組みが必要となる。

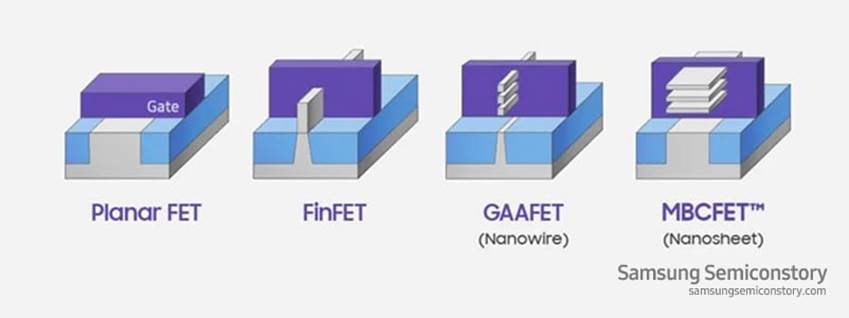

トランジスタ構造では、従来の平面型トランジスタ(プラナー型)から3次元構造のFinFETへと進化してきた。

さらに近年は、Gate-All-Around(GAA)FETと呼ばれる新たな構造が注目を集めている。

GAA FETとは、電流が流れる4面のチャネル全てをゲートが囲む構造を採用したトランジスタだ。

ゲートの接触面が従来の3面から4面に増やすことで、電流をより細かくコントロールし、電力効率を大きく向上させる仕組みとなっている。

GAA FETを用いたチップは、Samsung Electronicsが他社に先駆けて2022年に量産を開始した。

同社は、ナノシートを複数枚積層したGAA FET「MBCFET(Multi Bridge Channel FET)」を開発している。

Samsungの第1世代 3nm GAAプロセスは、同社の既存の5nmプロセスと比較して、消費電力が50%低減したという。

また、ノード面積が最大35%縮小し、性能も30%向上した。

さらに、TSMCも、2025年に製造開始予定の2nmプロセスでGAA FETを採用する計画となっている。

その他では、日本のRapidusもIBMの2nm GAA技術を用いた量産に向けて研究開発を進めている。

また、低消費電力化には素材選定も大きく影響する。

パワー半導体においては、ワイドバンドギャップ半導体のSiC(炭化ケイ素)やGaN(窒化ガリウム)が、高耐圧・低損失を可能にする素材として注目されている。

EV(電気自動車)や再生可能エネルギーを扱うインフラ設備などに広く導入され始めており、これらの新素材への投資や研究が活発化している。

さらに、チップ設計・実装技術も重要となる。3次元実装(3D積層)やチップレットアーキテクチャを活用し、複数のチップを高密度に接続してデータ伝送を効率化することで、消費電力の大幅な削減が期待できる。

特に、AIやクラウドサービスを支える大規模データセンターでは、このような高密度化技術が性能向上と省エネを両立する要となっている。

3.省エネ技術の動向

データセンターの高効率化は、世界的に大きな課題となっている。

サーバーの演算性能が年々飛躍的に向上する一方で、電力使用量の増加が避けられず、冷却のコストや環境負荷が深刻化している。

そこで、高効率なCPUやGPU、さらには専用のAIアクセラレータなど、計算を最適化するための省電力技術が続々と開発されている。

一方、IoT機器など小型デバイスにおいても、省エネ技術は最重要課題だ。

バッテリーで駆動するセンサーやエッジデバイスの場合、わずかな消費電力の違いが稼働時間に大きく影響する。

トランジスタの動作電圧を抑えながら性能を維持する設計や、必要な機能だけを最小限動作させるパワーゲーティングなどの技術が普及してきている。

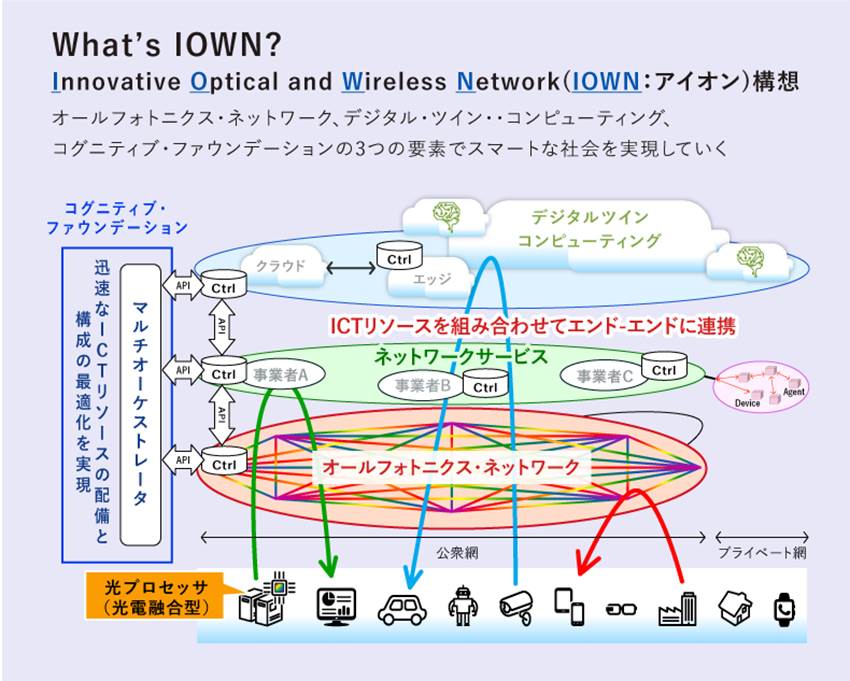

また、次世代の通信・演算技術として、光信号の活用が注目を集めている。

電気信号と比較して配線損失が少なく、伝送スピードが高速な光技術をチップ間やチップ内で用いることで、消費電力と発熱を削減しながらデータ処理の高速化を図る研究が進んでいる。

NTTが次世代通信基盤として開発を進めるIOWN(Innovative Optical and Wireless Network)構想においても、光電融合素子や光インタコネクト技術が鍵を握るとされており、日本政府が5年間の研究開発支援を発表している。

4.今後の課題と展望

半導体の微細化はムーアの法則に支えられてきたが、2nmプロセス以下の領域に突入すると、物理的・経済的なハードルがますます高くなる。

また、新素材の大規模な量産体制や、3D実装における実装コスト、歩留まり向上といった課題を克服しなければ、安定した低消費電力デバイスの普及は難しい。

一方で、高額な研究開発投資や大規模生産設備が必要となるため、各国政府による補助や支援は不可欠となる。

こうした支援策は、経済安全保障の観点からも重要であり、今後も継続される見通しだ。

さらに、低消費電力技術の開発には、材料工学や回路設計、ソフトウェア制御など幅広い領域の専門知識が求められる。

そのため、産学官が連携して人材育成・教育を進めることも大きなテーマとなる。

持続可能な社会の実現に向けて、半導体の消費電力削減は避けて通れない課題である。

デバイス構造の革新、新たな素材の導入、実装技術の高度化など、多面的なアプローチがこれまで以上に求められるだろう。

各企業や研究機関が連携し、低消費電力技術を開発・普及させることで、社会全体での省エネが大きく前進していくことが期待されている。

安部’s EYE

今回のトレンド情報は、「半導体の低消費電力化技術」と題してアップさせて頂く。

我々の生活において切っても切り離せないものになっている半導体だが、その活用と共に更に高性能化が進んでおり、伴って消費電力の増加も大きな課題となって来ている。

半導体の代表格となるトランジスタは、電気信号の“増幅”や“スイッチング”といった動作が主な役割になるが、一つのチップにどれだけ多くのトランジスタを集積出来るかで処理能力が変わってくることになる。

集積度を上げるためには微細化技術が必要になる訳だが、技術者の創意工夫と努力によって基本構造も進化しており、次々に微細限界の壁を突破し続けている。

その結果、膨大なデータ処理を可能とすると同時に圧倒的な消費電力低減も実現して来ている。

データ量の拡大によりデータセンターの普及も加速しているが、その消費電力は凄まじく技術革新が起きなければ2050年には現状比で130倍もの消費電力増加が予想されている。

従ってチップの発熱対策としての冷却方法や、高効率チップ等の省電力化技術の開発も進んでいる。

その中でも注目されているのが、電気信号に比べて圧倒的に消費電力を抑制できる“光信号の活用”である。

NTTが中心となって開発を進めている国産技術であり、大いに期待したいものである。

半導体の進化による利便性の向上だが、持続可能社会あってこそのものであり、そのためにも消費電力の削減に向けた取り組みと足並みを合わせた開発が必要と思われる。