TREND半導体業界トレンド情報

半導体業界トレンド情報

業界トレンド情報 第三十八弾 パッケージングの最新技術

1.2.5D(2.xD)パッケージング

生成AIやADAS(先進運転支援システム)、5G通信といったアプリケーションの台頭に伴い、半導体にはさらなる高集積化、高機能化が求められている。このような需要に対応すべく、前工程での微細化と合わせて注目を集めているのが先端パッケージング技術だ。

先端パッケージング技術の1つとして、2.5D(2.xD)パッケージングが挙げられる。

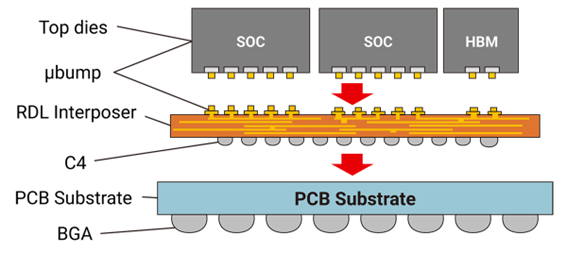

パッケージ基板の上にインターポーザと呼ばれる中間基板を置き、これを介してSoCやメモリといった半導体チップを接続するものだ。

代表的なものとして、TSMCが「CoWoS(Chip on Wafer on Substrate)」という名称で実用化している。

2.5Dパッケージングにより、チップを分割してそれぞれ最適なプロセスで製造できるため、性能の向上やコストの低減などが可能となる

インターポーザには、シリコンや有機RDL(再配線層)などが用いられる。

有機インターポーザは、シリコンインターポーザに比べてコストを抑えられる点がメリットとなる。

TSMCはシリコンインターポーザを用いた「CoWoS-S」に加えて、RDLを用いた「CoWoS-R」や、小型シリコンチップとRDLをともにインターポーザに用いた「CoWoS-L」を開発している。

なお、シリコンインターポーザを用いたものを2.5Dパッケージング、有機インターポーザを用いたものを2.1Dまたは2.3Dパッケージングと呼ぶこともあるため、これらを総称して2.xDパッケージングや2.nDパッケージングといった名称を用いることも多い。

2.HBM

先述の2.5Dパッケージングでは、メモリチップにHBMが用いられることが多い。

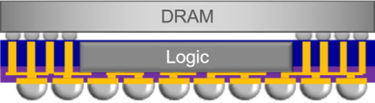

HBMとはHigh Bandwidth Memoryの頭文字を取ったもので、高い帯域幅を有するDRAMを指す。

DRAMチップを垂直に積層し、TSV(Through Silicon Via:シリコン貫通電極)という技術を用いて接続するものだ。

JEDEC(半導体技術協会)により規格化されている。

2024年時点で実用化されているものとしては、HBM3が最新となっている。

HBM3はデータ転送速度が1ピン当たり6.4Gビット/秒となっており、前世代のHBM2と比べて倍増した。

また、チャネル数もHBM2の8チャネルから16チャネルに倍増している。

1層あたりのメモリ容量は8〜32Gビットで、4層、8層、12層のメモリ積層に対応。

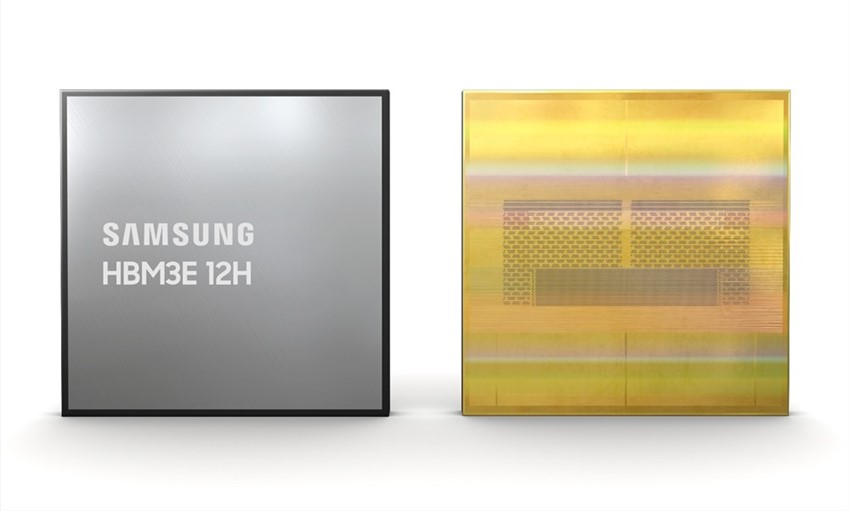

Samsungが2024年2月に発表した「HBM3E 12H」は12層で、容量が36Gバイト、転送速度が1280Gバイト/秒に達した。

なお、SK Hynixが、TSMCと共同で次世代規格となるHBM4の開発を進める計画を明らかにしている。

SK Hynixは、HBM3Eでは同社独自の技術を用いてベースチップを製造していたが、HBM4ではTSMCのロジックプロセスをベースチップに採用する予定だ。

2026年の量産開始を目指す。

3.FOWLP

FOWLPとは、Fan-Out Wafer Level Packagingの頭文字を取ったものだ。

ウエハープロセスを用いてRDLを形成する工程を特徴としている。

チップの外側にRDLが拡張した構造となっているため、数多くの入出力数に対応可能。

また、パッケージ基板を用いないためチップを薄くできる、製造コストを低減できる、配線長が短くなることで信号の伝送速度を高速化できるといったメリットがある。

FOWLPは、2000年代よりInfineon Technologiesが「eWLB」という名称で実用化していた。

その後2016年に、TSMCが開発したFOWLP技術「InFO」をiPhoneのモバイルプロセッサに用いたことで、本格的に注目を浴びることとなった。

現在では、ASEやJCETといった大手OSATもFOWLPの受託を開始している。

なお、ウエハーレベル以上に大型のパネルレベルで同様のパッケージングを行う技術も開発されており、FOPLP(Fan-Out Panel Level Packaging)と呼ばれている。

FOPLPは、Samsungがスマートウォッチ「Galaxy Watch」のプロセッサ製造で実用化している。

安部’s EYE

今回のトレンド情報は、「パッケージングの最新技術」についてアップさせて頂く。

半導体はウエハー状で回路形成を行う“前工程”と、ウエハーから個片化されたチップをパッケージングする“後工程”を経て製品化される。

熊本のJASMや北海道のRapidusは前工程の会社となり、数ナノメートルと言われる超微細加工を得意とする会社となり、“前工程”の高集積化は益々加速されて来ている。

伴って当然の如く“後工程”の方にも前工程の高集積化に対応する技術が必要になって来る訳だが、今回はその先端パッケージング技術について紹介する内容になっている。

記事にある通り、後工程においても前工程のウエハープロセスが用いられる様になって来ており、次第に従来の前工程と後工程の境界が無くなってきていることが分かると思う。

もっとも、これは最先端製品に用いられる技術ではあるが、将来的には従来までの後工程と言われる事業そのものの存在を根本から揺るがすものになる可能性もある。

1947年に半導体が生まれて77年になるが、また大きな歴史の転換期が近づいている気がする。