半導体業界トレンド情報

業界トレンド情報 第三十一弾 半導体のチップレット化動向

1.チップレットとは?

半導体の最先端プロセスにおいては、現在もさらなる微細化に向けた取り組みが続いている。

微細化の切り札とされつつ、かつては実用化への障壁が高かったEUV露光装置も、今ではデバイスメーカー大手数社により量産適用されている。

また、従来のFinFET構造の性能限界を打破すべく、Samsung Electronicsが開発を進めているGAA(Gate-All-Around)など、新しいトランジスタ構造を模索するケースなどもみられる。

このような取り組みにより、微細化に向けた研究開発が依然進行しているものの、そのハードルがどんどん高くなっているのも事実である。

最先端となる3nmプロセスの量産立ち上げを進めているのは、TSMCとSamsung Electronicsの2社のみとなった。

かつては微細化競争でしのぎを削っていたIntelも、3nmプロセスではTSMCに製造を委託する模様だ。

微細化が困難を極める中、半導体のさらなる性能向上に資するとして近年注目を集めている技術がチップレットである。

半導体の製造プロセスは、通常1枚の半導体ウエハ(基板)の上にパターンを形成し、これをダイシング(分割)することで複数のチップを作製するものとなっている。

このため、1チップの中にCPUやGPU、メモリなどさまざまな機能を含めたSoC(System on Chip)であっても、単一のウエハ、単一のテクノロジーノードで製造していた。

これに対して、異なるウエハやテクノロジーノードでCPUやGPU、メモリなどをパーツとして製造し、後にこれらをパッケージ基板上で電気的につなぎ合わせることで、SoCを構成する技術が存在する。

この技術における一つ一つのパーツが、チップレットと呼ばれるものとなる。

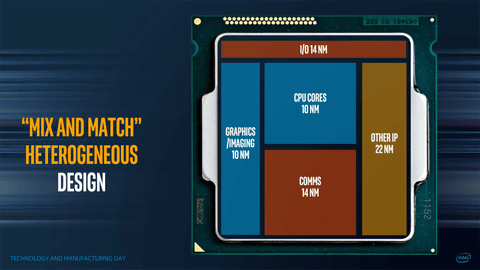

チップレットのイメージ 出所:Intel

2.チップレットのメリット

処理能力への要求の高まりを受けて、SoCの搭載コア数も増え続けている。

このため、サーバー用の先端SoCになると、コア数とともにチップ面積も巨大化している。

このようなSoCを従来の方式で製造しようとすると、歩留まりが低くなってしまうのが問題となる。

基本的に、歩留まりとチップ面積は負の相関にあるからだ。

これにより、1ウエハから得られる良品チップの数が減少し、コストの増大に繋がることとなる。

一方で、チップレットを用いる場合、分割したチップレットのみを製造すれば良いため、チップ面積が縮小することで歩留まりが向上する。

このため、コストを抑えることが可能となる。

また、チップレットを用いることで、各機能に適したテクノロジーノードを使用できることとなる。

プロセッサコアなどには、最先端ノードを使用することで性能向上を図りながら、最先端ノードによる利益をあまり得られないI/Oデバイスなどには、よりレガシーなノードを用いるといったような使い分けが可能となる。

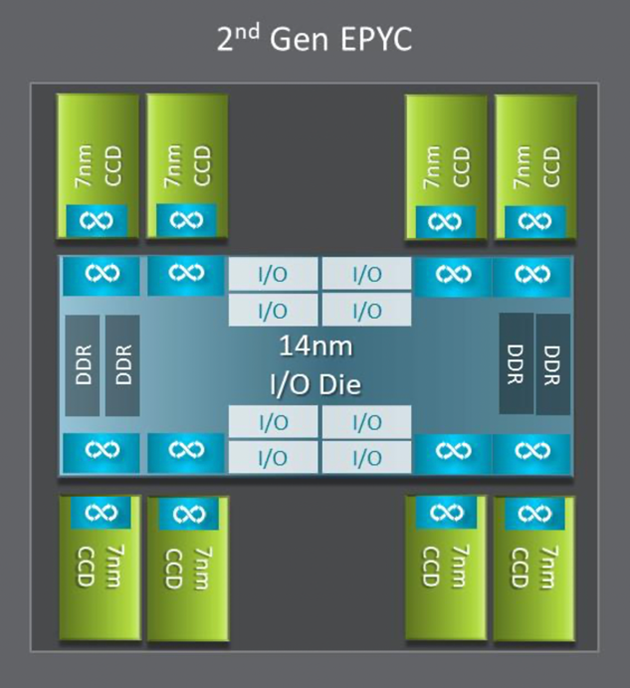

AMDのマイクロプロセッサ「EPYC」の構成図 出所:AMD

単一の機能のみをパーツとして生産できるため、設計も容易となる。

さらに、他社の作製したチップを含めることもできるため、各社の得意分野を取り込んだチップ製造が可能となる。

3.チップレットに関する動向

AMDは2019年、チップレットを用いた同社のサーバー用マイクロプロセッサ「EPYC」の第2世代品を発表している。

上の画像のように、7nmプロセスを用いたCCD(CPU Complex die)と14nmプロセスを用いたIOD(I/O die)が1チップに収まるものとなった。

また同社は、クライアントPC向けのマイクロプロセッサ「Ryzen」にもチップレットを用いている。

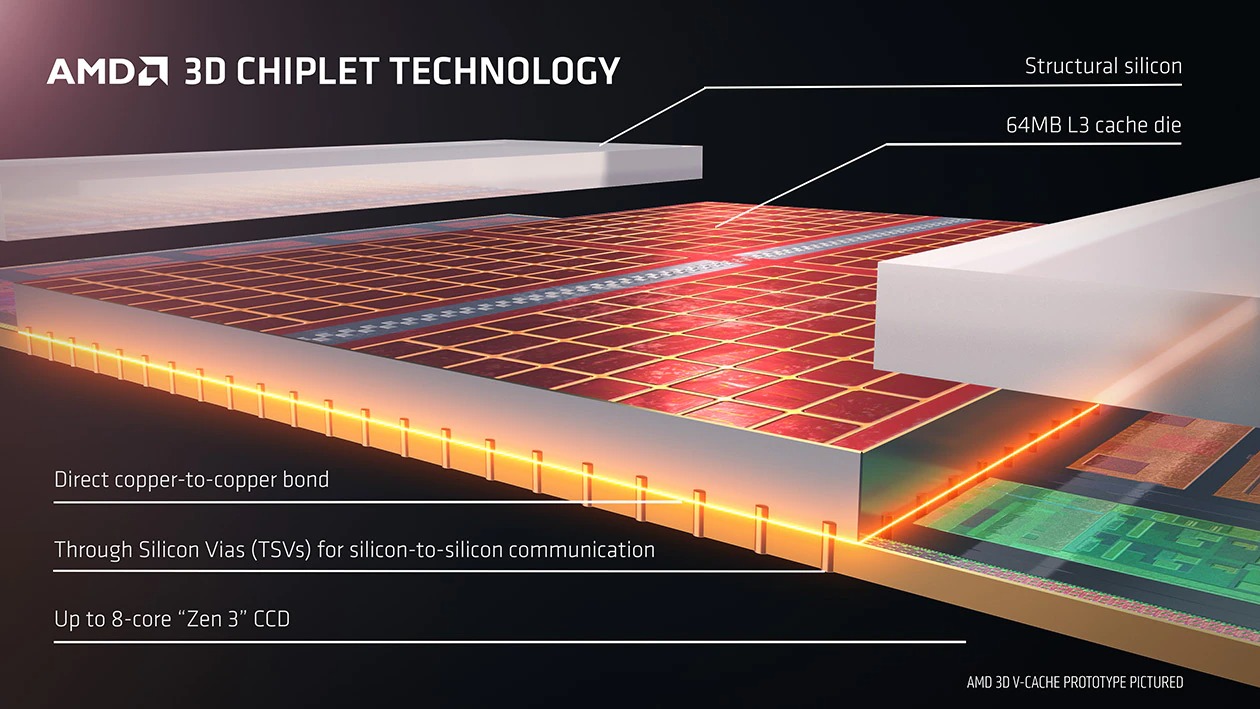

チップレットを垂直方向に積層する技術「3D V-Cache Technology」を2021年5月に発表しており、同技術を用いた「Ryzen 7 5800X3D」を2022年4月に発売した。

同製品は、CCDの上に64MBのL3キャッシュメモリを積層し、TSVを用いて接続した構造となっている。

AMDの発表によると、2Dチップレットと比較して、相互接続密度が200倍以上に向上したという。

3Dチップレット技術のイメージ 出所:AMD

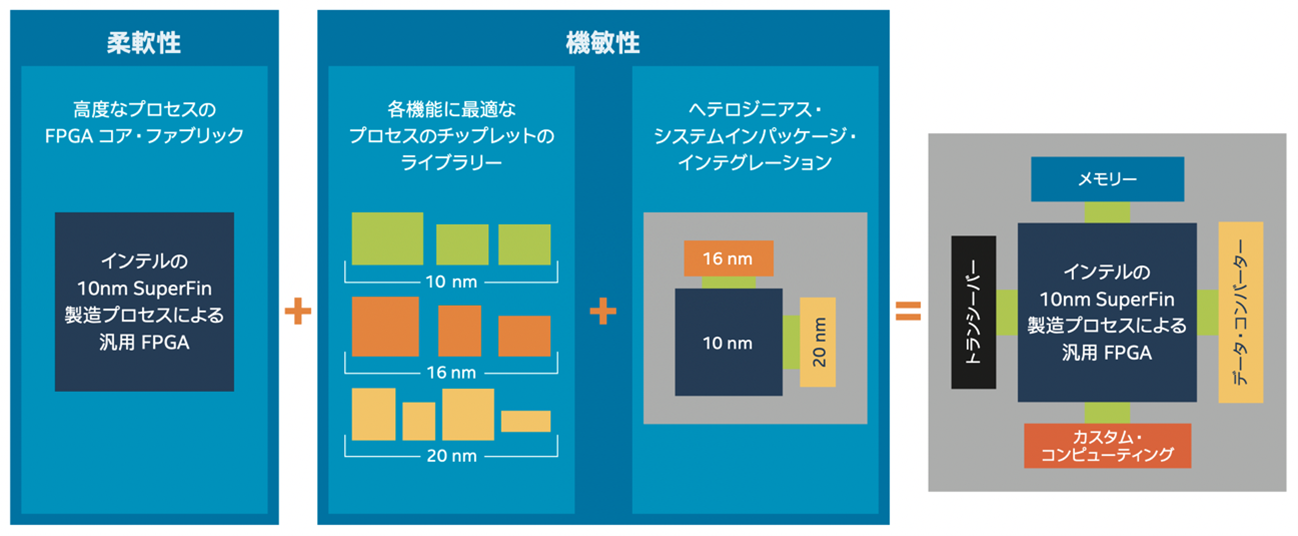

また、Intelも2019年、チップレットを用いた10nmプロセスFPGA「Agilex」を発表した。

10nmプロセスを用いたFPGAチップレットの他に、16nmプロセスや20nmプロセスを用いたメモリやトランシーバーなどのチップレットを組み込んでいる。

Intelのチップレットを用いたFPGA「Agilex」の構成イメージ 出所:Intel

このようにチップレットを実際の製品に用いているAMDおよびIntelは、2022年3月に業界団体「Universal Chiplet Interconnect Express」(UCIe)を設立したと発表した。

その他にも、Samsung Electronics、TSMC、ASE、arm、Google Cloud、Meta、Microsoft、Qualcommと計10社が参画している。

UCIeのロゴ 出所:UCIe

同団体は、チップレット間の通信(インターコネクト)を標準化するもので、設立発表と同時に標準仕様として「UCIe 1.0」を発表した。

今回の団体設立および標準仕様の発表により、チップレットを用いたSoCの開発および製品化が、会社の垣根を越えてさらに活発化することが期待される。

今回のトレンド情報は、「半導体のチップレット化動向」についてアップさせて頂く。

記事にもある通り、半導体の更なる性能向上を目的とした微細化については、留まることのない研究開発が世界中で進められている。

現在最先端となる3nmプロセスの量産立上げを進めているのは、台湾のTSMCと韓国のSamsung Electronicsの2社のみとなっており、如何に技術的な難易度と投資負担が大きいかを物語る証である。

半導体の微細化については、更なる要求も高まって来るとともに、対する技術のブレークスルーも必ずや実現されては来ると思われるが、今回は微細化技術の壁打破に対する一つの解となる「チップレット」に関する情報を分かり易く紹介するものである。

チップレットの考え方は以前より存在はしていたが、いよいよ各社とも本格的な採用が加速してきている。

その中で注目すべきことが、チップレットを製品に用いる標準化を進めるための業界団体「Universal Chiplet Interconnect Express」(UCIe)が設立されたことである。

現時点では世界で10社が参画しているが、日本企業の名前が入っていないのが残念ではある。

しかしチップレットにより、上記した2社以外の会社も各社の得意分野が生かせる可能性が出て来た事は間違いなく事実であり、会社や国家の垣根を越えた更なる活性化を期待したい!